Google в сотрудничестве с производственными компаниями SkyWater Technology и Efabless запустил инициативу, позволяющую разработчикам открытого аппаратного обеспечения бесплатно изготовить развиваемые ими чипы. Инициатива нацелена на стимулирование развития открытого аппаратного обеспечения, сокращение издержек при разработке открытых проектов и упрощение взаимодействия с заводами, осуществляющими производство. Благодаря инициативе любой желающий может начать разрабатывать собственные специализированные чипы, не опасаясь больших издержек на производство начальных прототипов. Все затраты на производство, упаковку и доставку берёт на себя Google.

Заявки на включение в программу бесплатного производства можно отправлять раз в два месяца. Ближайший слот будет закрыт 8 июня, а успевшие попасть в него чипы будут готовы 30 августа и отправлены авторам 18 октября. Заявки принимаются только от проектов полностью распространяемых под открытыми лицензиями, не обременённых соглашениями о неразглашении (NDA) и не ограничивающими область использования своих продуктов. Данные для производства должны передаваться в формате GDSII, проходить предоставляемый тестовый набор и воспроизводиться из исходных проектных файлов (т.е. заявить открытый проект, а передать для производства макет проприетарного не получится).

Для упрощения разработки открытых чипов предлагаются следующие открытые инструменты:

- SkyWater PDK (Process Design Kit), инструментарий, описывающий используемый на заводе SkyWater техпроцесс 130nm (SKY130) и позволяющий подготовить необходимые для производства микросхем проектные файлы.

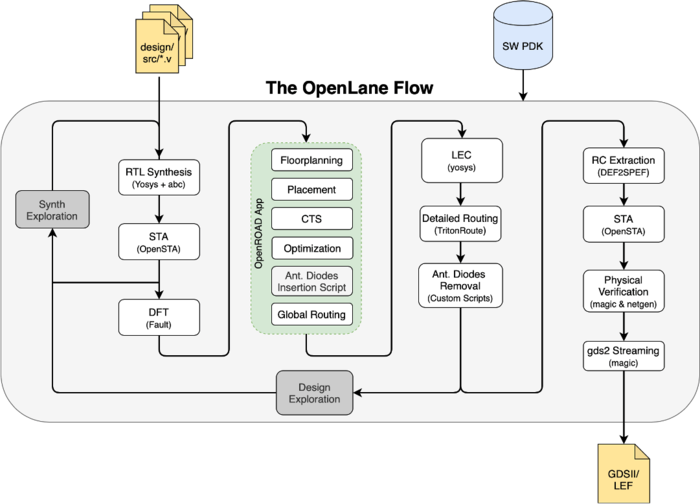

- OpenLane – набор компонентов для автоматизированного преобразования RTL-схемотехники специализированных чипов (ASIC) в формат GDSII, используемый на фабриках для изготовления микросхем.

- XLS (Accelerated HW Synthesis) – инструментарий для синтеза проектных файлов с аппаратной ничинкой чипов, соответствующих предоставленному высокоуровневому описанию необходимой функциональности, оформленному в стиле разработки программного обеспечения.

- Набор правил для сборочной системы Bazel с поддержкой открытых инструментов (Yosys, Verilator, OpenROAD) для работы с языками описания оборудования (Verilog, VHDL, Chisel, nMigen).

- OpenROAD – фреймворк для автоматизации процесса разработки открытых микросхем.

- Verible – набор инструментов для разработки на языке Verilog, включая парсер, систему форматирования стиля и linter.