Проект Libre-SOC, развивающий открытый ASIC-чип с реализацией гибрида, в котором CPU, VPU и GPU не разделены и предложены как единое целое в стиле архитектуры CDC 6600, достиг стадии передачи в производство первого тестового образца. Изначально проект развивался под именем Libre RISC-V, но был переименован в Libre-SOC после решения заменить RISC-V на использование архитектуры набора команд (ISA) OpenPOWER 3.0.

Проект нацелен на создание полноценной, полностью открытой и не требующей лицензионных отчислений системы на чипе (SoC), которую можно будет использовать в одноплатных компьютерах, нетбуках и различных портативных устройствах. Помимо свойственных CPU инструкций и регистров общего назначения, Libre-SOC предоставляет в одном функциональном блоке процессора возможности для выполнения векторных операций и специализированных вычислений, свойственных VPU и GPU. Чип использует архитектуру набора команд OpenPOWER, расширение Simple-V c инструкциями для векторизации и параллельной обработки данных, а также специализированные инструкции для преобразования в ARGB и выполнения типовых 3D-операций.

Функции GPU сосредоточены на предоставление аппаратного ускорения графического API Vulkan, а VPU на ускорение преобразования YUV-RGB и декодирования форматов MPEG1/2, MPEG4 ASP (xvid), H.264, H.265, VP8, VP9, AV1, MP3, AC3, Vorbis и Opus. Для Mesa развивается свободный драйвер, который использует возможности Libre-SOC для предоставления аппаратно ускоренной программной реализации графического API Vulkan. Например, шейдеры Vulkan могут быть транслированы при помощи JIT-движка для выполнения с использованием доступных в Libre-SOC специализированных инструкций.

В следующем тестовом прототипе планируется реализовать векторное расширение SVP64 (Variable-length Vectorisation), позволяющие использовать Libre-SOC в качестве векторного процессора (помимо 32 64-разрядных регистров общего назначения будет предоставлено 128 регистров для векторных вычислений). Первый прототип включает только одно ядро, работающее на частоте 300 Mhz, но в течение

двух лет планируется выпустить 4-ядерную версию, затем 8-ядерную, а в долгосрочной перспективе и 64-ядерную.

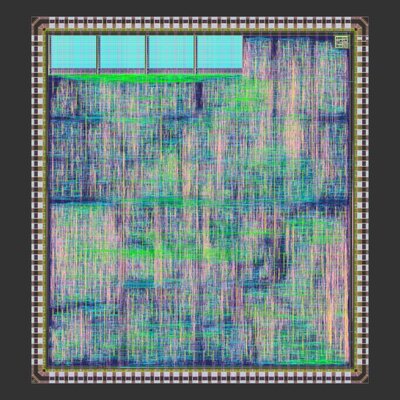

Первая партия чипа будет произведена в компании TSMC с использованием техпроцесса 180nm. Все наработки проекта распространяются под свободными лицензиями, в том числе доступны файлы в формате GDS-II с описанием полной топологии чипа, достаточной для начала собственного производства. Libre-SOC станет первым полностью независимым чипом на базе архитектуры Power, произведённым не компанией IBM. При разработке использовался язык описания аппаратуры nMigen (HDL на базе Python, без использования VHDL и Verilog), библиотеки стандартных ячеек FlexLib от проекта Chips4Makers и свободный VLSI-инструментарий Coriolis2 для преобразования из HDL в GDS-II.

Разработка Libre-SOC была профинансирована фондом NLnet Foundation, который выделил 400 тысяч евро на создание полностью открытого чипа в рамках программы по созданию верифицируемых и заслуживающих доверия фундаментальных технических решений.

Чип имеет размер 5.5×5.9 мм^2 и включает 130 тысяч вентилей. В состав входит четыре модуля SRAM по 4КБ и 300 MHz блок фазовой автоподстройки частоты (PLL).